The problem isn’t that standardized IP is bad. It was designed for the middle of the market. If your design sits at the edge of what’s possible in performance, power, or area, the middle of the market isn’t where you need to be.

In many advanced designs, even small inefficiencies in IP—such as extra logic, unused features, or suboptimal configurations—can directly impact performance, power, and silicon cost.

As semiconductor designs grow more complex, the gap is widening between what standardized IP delivers and what cutting-edge chips actually need. AI accelerators, edge computing devices, smart vehicles, AIoT hardware, and wearables all demand higher performance, lower power, and smaller silicon footprints than ever before. Standard IP blocks, built for broad compatibility, often can’t hit all three.

That’s why customizable IP—often referred to as custom IP or configurable IP—is no longer a nice-to-have. SoC IP customization is becoming a core part of how leading semiconductor teams compete.

The Limits of One-Size-Fits-All Standard IP

Standardized IP has real value. It’s pre-verified, broadly compliant, and fast to integrate. For many applications, it’s exactly the right choice.

But for teams pushing the boundaries of performance and efficiency, generic IP creates friction. It carries features you don’t need, imposes constraints your architecture didn’t ask for, and leaves PPA (power, performance, and area) optimization on the table.

When you’re designing for a specific workload, interface, or power envelope, that overhead adds up.

The areas where this matters most are memory interfaces, on-chip interconnects, and high-speed connectivity protocols—precisely where performance, power, and area tradeoffs are most critical.

Customization enables design teams to:

- Eliminate unnecessary features to reduce silicon area

- Optimize performance for targeted workloads

- Modify protocol configurations to suit specific system architectures

- Improve power efficiency

- Align IP capabilities with distinct product requirements

Customization Is Harder Than It Looks

The appeal of custom IP is obvious—tailor the implementation, remove unnecessary features, and hit your targets. In practice, it’s more complicated.

Effective customization goes far beyond parameter changes. It often requires architectural modifications, protocol adjustments, and full re-verification.

Consider what’s involved in real-world scenarios:

- Changing an SoC bus interface (e.g., AXI to AHB) requires rearchitecting communication, not just updating a configuration

- Adding an internal DMA block involves new hardware design and full verification of data paths

- Protocol extensions may require non-standard implementations and custom validation

- Reducing gate count often requires stripping IP down to only essential functionality

In safety-critical domains like automotive, aerospace, medical, and industrial systems, functional safety requirements add another layer of complexity.

Custom IP done well requires deep protocol expertise, a rigorous development process, and verification infrastructure that can validate every modification.

SmartDV’s Answer: IP Your Way

Customization isn’t a side offering at SmartDV—it’s central to how the company operates.

The idea behind IP Your Way is simple: customers shouldn’t have to adapt their designs to fit available IP. The IP should fit the design.

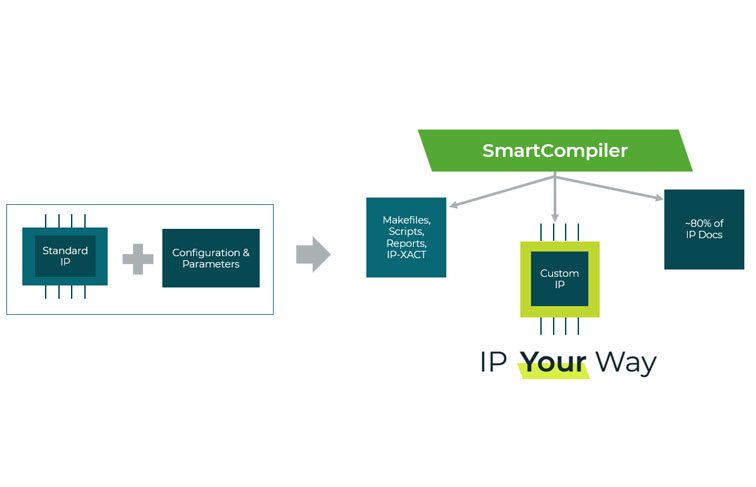

SmartDV brings together a portfolio of design IP and verification IP, along with nearly 1,000 person-years of engineering experience and a proprietary development platform called SmartCompiler™.

The result is customized IP that is standards-compliant, production-ready, and optimized for each customer’s specific requirements.

SmartCompiler™: The Engine Behind the Customization

SmartCompiler™ automates and streamlines the lifecycle of IP development, customization, and verification.

Instead of manually modifying RTL for each requirement, SmartCompiler generates IP variants efficiently and consistently, with full verification applied to each configuration.

SmartCompiler enables:

- Faster development cycles (months reduced to weeks)

- Reduced engineering overhead

- Consistent protocol compliance

- Optimized and repeatable IP generation

How the SmartDV Customization Process Works

SmartDV’s workflow is built around three key stages:

1. Start With the Right Foundation

Customers select from SmartDV’s portfolio of interface IP and verification IP. Where needed, SmartDV extends or adapts IP to meet specific design requirements.

2. Define What You Actually Need

Requirements are defined upfront, including PPA targets, interface specifications, and system constraints. This ensures the final IP is optimized for the design.

3. Customize, Verify, Integrate

SmartDV engineers customize the IP using SmartCompiler, then validate it using comprehensive verification methodologies.

For complex systems—such as combining a DDR5 memory controller with a PCIe Gen 6 interface—SmartDV also provides pre-integration support.

Explore the full Design IP and Verification IP portfolio.

Built for What’s Next

More than 450 customers worldwide rely on SmartDV IP to accelerate development.

Emerging trends such as chiplet architectures, AI silicon, and heterogeneous integration are increasing demand for customized IP. Generic IP often cannot meet the performance and efficiency requirements of these systems.

Frequently Asked Questions About Custom IP

What is custom IP in semiconductor design?

Custom IP refers to design or verification IP that is modified or built to meet specific system requirements. Unlike standard IP, it is optimized for performance, power, area (PPA), and architectural constraints.

How is customizable IP different from standard IP?

Standard IP is built for broad compatibility, while customizable IP is tailored to a specific design. Custom IP removes unnecessary features, improves efficiency, and aligns with the exact requirements of the SoC.

Why is PPA optimization important in SoC design?

PPA (power, performance, and area) determines the efficiency and cost of a chip. Optimizing PPA helps improve speed, reduce energy consumption, and minimize silicon footprint, which is critical in modern applications like AI and edge devices.

When should a design team choose custom IP?

Custom IP is most valuable when standard IP cannot meet performance, power, or architectural requirements. This is common in high-performance computing, AI hardware, and specialized SoC designs.

Does custom IP require additional verification?

Yes. Any customization—such as architectural changes or protocol modifications—requires full verification to ensure functionality, compliance, and reliability are maintained.

As designs become more specialized, customizable IP is becoming a key differentiator in chip development.

Stop Working Around IP That Doesn’t Fit

Get IP built for your architecture, optimized for your PPA.

» Explore Custom IP Solutions

» Browse Design IP

» Browse Verification IP

» Contact SmartDV