Blog by Erik Panu, Chief Business Officer, SmartDV

There are a lot of perks to living in the Bay Area—mild weather, diverse culture, and beautiful nature, just to name a few—but this week gave me the opportunity to take advantage of one in particular: regular attendance at a wide variety of semiconductor industry conferences.

Temporarily trading the serenity of the Santa Cruz Mountains for the energy of Silicon Valley, I spent last Tuesday and Wednesday at the annual

RISC-V Summit

in Santa Clara. In case you weren’t able to attend, I’d like to share a few of my top takeaways from what I found to be an edifying and even eye-opening event.

Day 1: Tuesday, November 7th

I devoted much of Day 1 to attending the keynotes and sessions. Here are some of the highlights:

1. Calista Redmond, CEO, RISC-V International

Calista shared RISC-V International’s vision clearly and succinctly: “This is a wholistic business strategy.” RISC-V International aims to enable its constituents to elevate industry leadership, build a strategic network, achieve business ROI, and gain technical advantage.

Analyst findings I found most salient:

- RISC-V will be in more than 16 billion SoCs by 2030

- RISC-V stands to capture 27% of automotive AI acceleration by 2030

- RISC-V will command 28% of the IoT market by 2025, with ~20B IoT cores shipped by 2028

All of this points to a vibrant, thriving, and growing RISC-V ecosystem—the

landscape

is well worth a look.

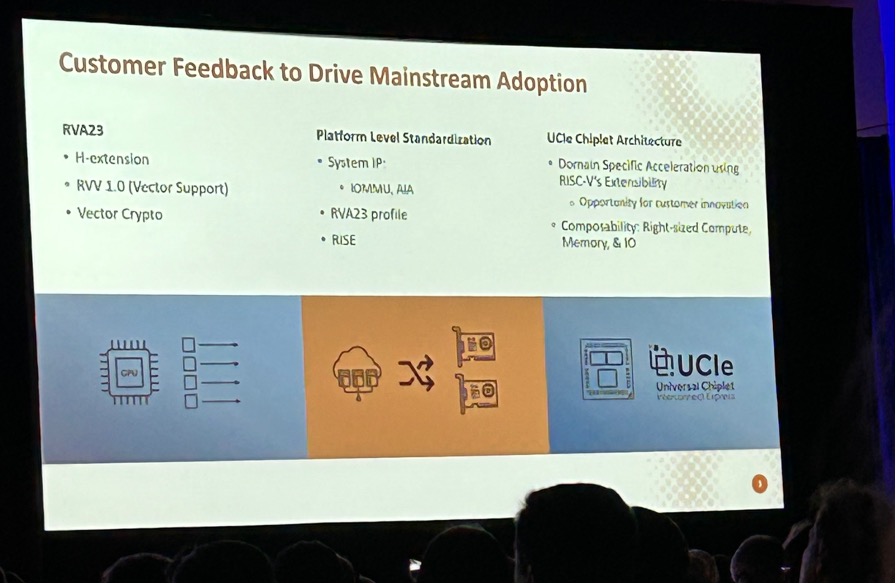

Balaji Baktha, Founder & CEO, Ventana Micro Systems

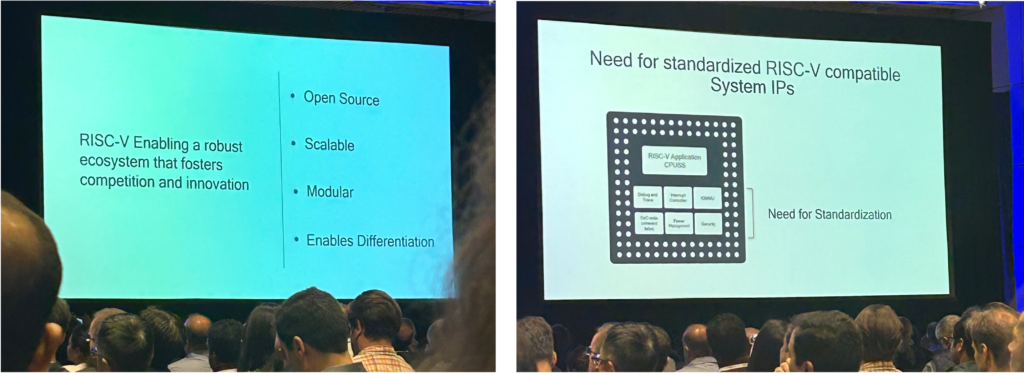

Two points stood out: “RISC-V architecture fits chiplet architecture perfectly,” and Google will treat RISC-V as a major ISA in client devices.

Customer adoption is making RISC-V mainstream: it now drives process conversations with capabilities and flexibility single-vendor ecosystems can’t match.

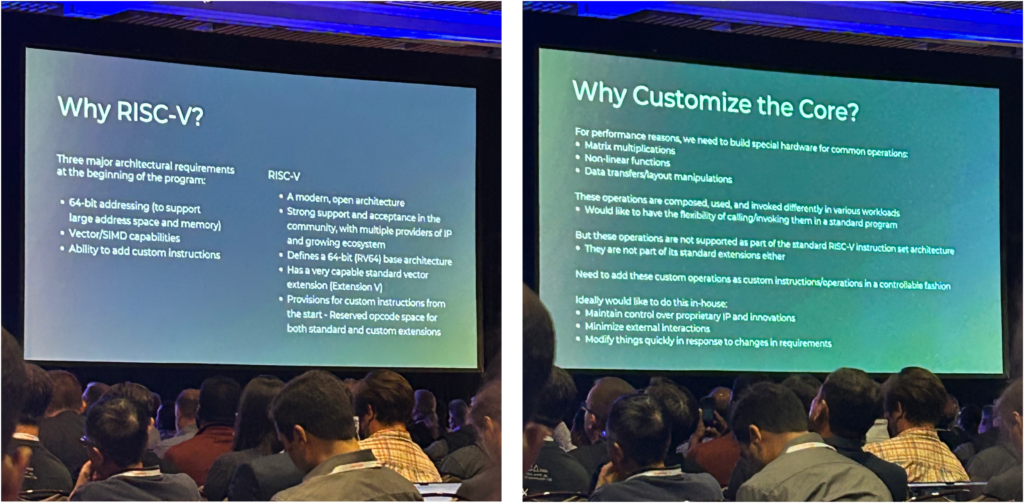

Prahlad Venkatapuram, Senior Director of Engineering, Meta

RISC-V’s differentiator is customization—custom instructions and extensions enable performance and optimization. His ask of IP vendors: embrace customization, ensure seamless interoperability, and provide robust debug.

- A robust ecosystem to support commercial success

- Standard specifications for customization (with encoding space)

- Peripheral IP tested with RISC-V cores (e.g., the

SmartDV–Codasip companion IP)

Ziad Asfhar, SVP Product Management, Qualcomm

- “$700B addressable edge device market in next decade”

- “Qualcomm shipped 650 million devices in 2022”

- “Customization lets us focus on the consumer’s experience”

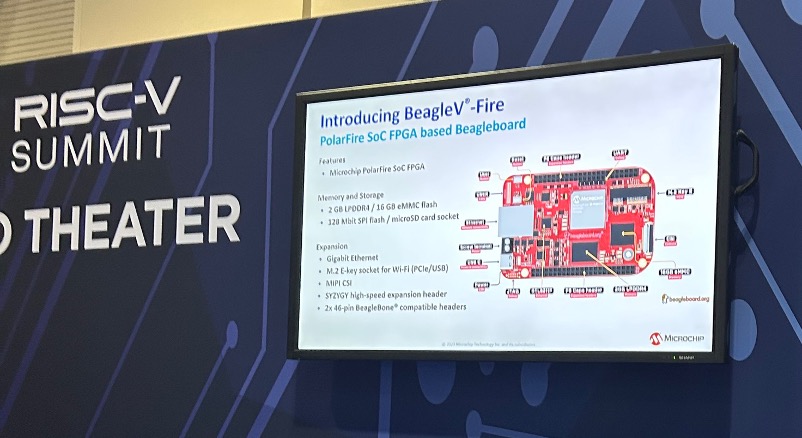

Later, I caught Microchip’s Demo Theater session on the BeagleV-Fire (PolarFire SoC FPGA based Beagleboard).

Day 2: Wednesday, November 8th

I shifted my focus to the ecosystem. SmartDV has carved out a niche via strategic IP partnerships (Codasip, NSI-TEXE, and more). Codasip, a platinum sponsor, was everywhere—great chance to deepen ties.

I started with Codasip CEO Ron Black’s keynote on processor security and CHERI—an industry-first commercial implementation.

Learn more about CHERI

here

and Codasip’s announcement

here.

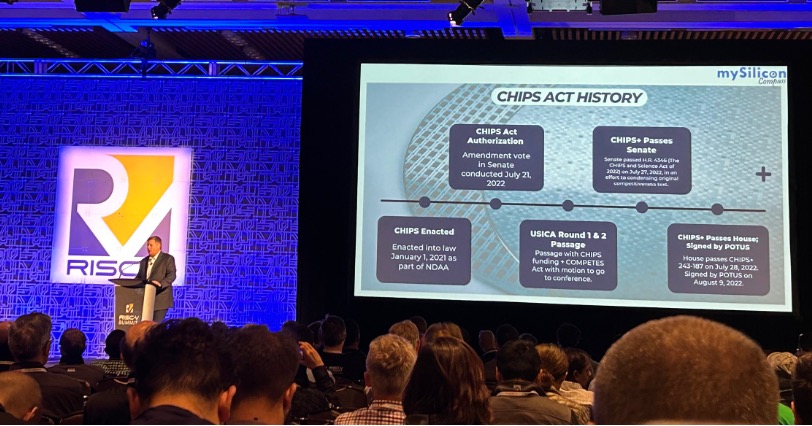

Also notable: keynote from the Honorable Ian Steff (CHIPS Act insights).

In the exhibit hall I spent time with Codasip’s team (many from Europe) and checked out their latest

Custom Compute

demo featuring SmartDV peripheral IP.

Customers continue to respond enthusiastically to our joint offering—busy booth! One-stop licensing of a RISC-V processor and companion peripheral IP removes friction for design and verification teams.

Two additional themes emerged:

1) As standards mature, software drivers will be a key need (especially with customization). Vendors must work closely with users.

2) Verification: strong standards verification will be essential (ecosystem still maturing).

In Summary

RISC-V isn’t going anywhere—momentum is undeniable.

The takeaway: RISC-V processors offer unprecedented flexibility to tailor products to end-user needs. IP providers must support interface changes and customization. Custom IP is no longer optional—it’s vital.

SmartDV’s customizable design IP and VIP are ideal complements to RISC-V. Gone are the days of rigid, one-size-fits-all IP. With SmartDV, you gain a trusted partner whose engineers become an extension of your team to achieve the precise functionality and PPA you need.

Ready to get started with RISC-V processors and customized IP? SmartDV can help! Learn more at

smartdvtech.com/services_customized_ip/.

About Erik Panu

Erik Panu leads the North American and European businesses for SmartDV, heading a team of sales, marketing, and technical professionals who support customer engagements, press/media, events, and company operations. Erik’s past roles—as GM of the Cadence IP Group and business leader at AI startups including BabbleLabs—position him to scale SmartDV’s business to better serve customers. He lives with his family in the Santa Cruz Mountains of California.